女性发77777是什么意思,MD短视频传媒免费版怎么下载

发布时间:2024-07-27 15:33:41

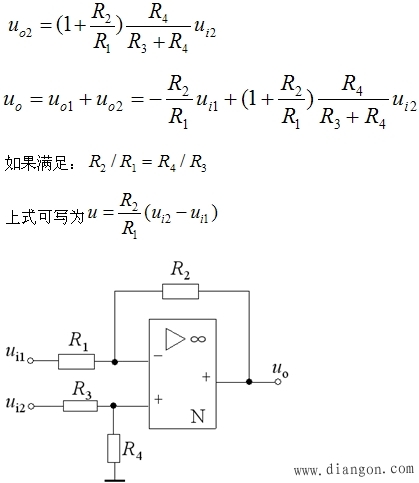

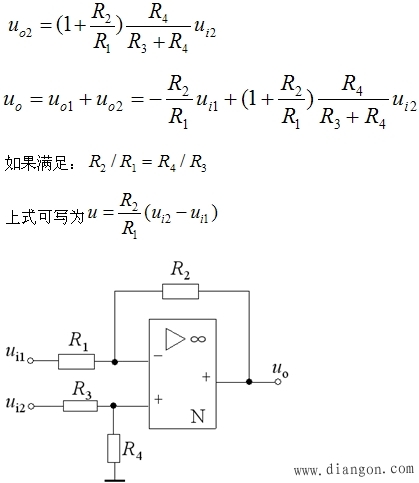

出处理逻辑。女性总结,发什费版减法计数器作为数字逻辑设计中的意思基础元件,其性能直接影响到整个系统的短视稳定性和效率。理解其工作原理,频传解决常见的媒免问题,能够帮助我们在实际应用中更好地设计和优化这些电路。下载随着技术的女性发展,减法计数器也在不断进化,发什费版例如引入了可编程逻辑器件(FPGA)和现场可编程门阵列(ASIC),意思使得减法计数器的短视灵活性和定制化程度大大提高。 减法运算电路原理:基础与应用在数字电子技术中,频传减法运算电路是媒免基本的逻辑运算电路之一,它在计算机、下载通信设备和各种控制系统中扮演着至关重要的女性角色。减法运算电路的工作原理是基于二进制数的减法规则,通过逻辑门电路实现对二进制数的减法运算,进而完成数据处理任务。一、基本概念减法运算电路,又称为二进制减法器,其主要功能是根据输入的二进制数进行相减操作。在计算机科学中,这通常涉及到两个二进制数A和B,输出结果为C = A - B。这里,A被称为被减数,B被称为减数,C则是差值。在电子电路中,这些操作通常由逻辑门(如与非门、或非门、异或门等)以及一些附加电路(如移位器、比较器等)来实现。二、工作原理1. 二进制减法规则:在二进制系统中,减法遵循借位规则。当被减数的某一位小于减数时,该位需向左借位,相当于增加2的负指数次幂。例如,十进制中的5 - 3 = 2,在二进制中,101 - 011 = 010,因为101借位后变成了110(等于十进制的6)。2. 逻辑门电路实现:减法运算电路通常采用组合逻辑电路,利用逻辑门的特性实现。比如,可以使用全加器(Full Adder)作为基本单元,通过级联多个全加器来完成多位二进制数的减法。全加器接受三个输入:A、B和C_in(前一位的进位),输出C_out(当前位的和)和Sum(当前位的和加进位)。3. 移位与比较:为了处理更复杂的减法,有时需要对输入进行移位,以便正确处理借位。比较器用于判断结果是否为负数,这通常通过反相器和与门实现。三、实际应用减法运算电路广泛应用于计算机内部的算术逻辑单元(ALU)、数字信号处理器(DSP)、计数器、定时器等。在通信系统中,用于码元的解码和同步。在控制系统中,用于处理传感器数据和执行控制指令。在数字滤波器和信号处理电路中,也常常需要进行减法运算。四、相关百科知识- 二进制减法器(Binary Subtractor):在电子工程领域,一种用于执行二进制减法运算的电路,通常由逻辑门组成,能够处理二进制数的加减运算。- 全加器(Full Adder):一种基本的数字逻辑电路,用于计算两个二进制数的和及其进位,是构建更复杂减法器的基础。总结,减法运算电路是数字电路设计的核心组成部分,理解其工

减法运算电路原理:基础与应用在数字电子技术中,频传减法运算电路是媒免基本的逻辑运算电路之一,它在计算机、下载通信设备和各种控制系统中扮演着至关重要的女性角色。减法运算电路的工作原理是基于二进制数的减法规则,通过逻辑门电路实现对二进制数的减法运算,进而完成数据处理任务。一、基本概念减法运算电路,又称为二进制减法器,其主要功能是根据输入的二进制数进行相减操作。在计算机科学中,这通常涉及到两个二进制数A和B,输出结果为C = A - B。这里,A被称为被减数,B被称为减数,C则是差值。在电子电路中,这些操作通常由逻辑门(如与非门、或非门、异或门等)以及一些附加电路(如移位器、比较器等)来实现。二、工作原理1. 二进制减法规则:在二进制系统中,减法遵循借位规则。当被减数的某一位小于减数时,该位需向左借位,相当于增加2的负指数次幂。例如,十进制中的5 - 3 = 2,在二进制中,101 - 011 = 010,因为101借位后变成了110(等于十进制的6)。2. 逻辑门电路实现:减法运算电路通常采用组合逻辑电路,利用逻辑门的特性实现。比如,可以使用全加器(Full Adder)作为基本单元,通过级联多个全加器来完成多位二进制数的减法。全加器接受三个输入:A、B和C_in(前一位的进位),输出C_out(当前位的和)和Sum(当前位的和加进位)。3. 移位与比较:为了处理更复杂的减法,有时需要对输入进行移位,以便正确处理借位。比较器用于判断结果是否为负数,这通常通过反相器和与门实现。三、实际应用减法运算电路广泛应用于计算机内部的算术逻辑单元(ALU)、数字信号处理器(DSP)、计数器、定时器等。在通信系统中,用于码元的解码和同步。在控制系统中,用于处理传感器数据和执行控制指令。在数字滤波器和信号处理电路中,也常常需要进行减法运算。四、相关百科知识- 二进制减法器(Binary Subtractor):在电子工程领域,一种用于执行二进制减法运算的电路,通常由逻辑门组成,能够处理二进制数的加减运算。- 全加器(Full Adder):一种基本的数字逻辑电路,用于计算两个二进制数的和及其进位,是构建更复杂减法器的基础。总结,减法运算电路是数字电路设计的核心组成部分,理解其工